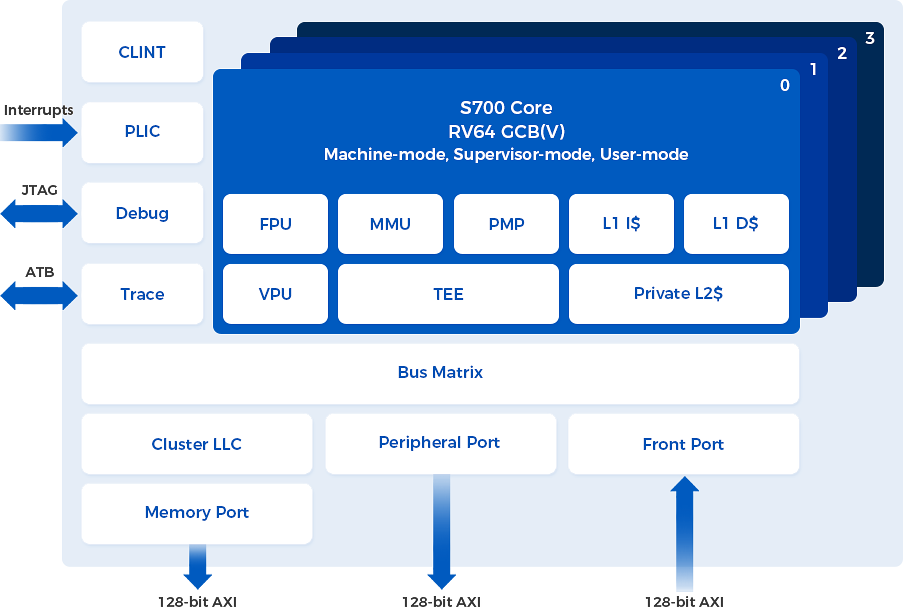

S700 integrates self-developed 9~12-stage pipeline, 3-way decoding, multiple-issue and out-of-order architecture.

It can be composed into a cache coherence subsystem with three levels of cache layers and up to four cores.

Trusted execution environment and optional E-Trace for advanced debugging function is supported.

Linux and various operating systems are available, which can be widely used in high-performance scenarios such as mobile phone processors and application processors.

| Features | Description | ||||

| ISA | RV64 GCB(V) | ||||

| Multi-core | single core, dual core, 4 core option available | ||||

| Modes | Machine-mode, Supervisor-mode, User-mode | ||||

| Security | supporting ESWIN TEE solutions, with up to 64 PMP regions | ||||

| Pipeline | 12-stage superscalar out-of-order pipeline, 3-way decode | ||||

| Branch Predictor | BTB, IJTB, BHT, RAS | ||||

| L1 I$ | configurable sizes from 16KB to 64KB, Parity/ECC optional | ||||

| L1 D$ | configurable sizes from 16KB to 64KB, Parity/ECC optional | ||||

| Private L2$ | configurable sizes from 0KB to 512KB, Parity/ECC optional | ||||

| Cluster LLC | configurable sizes from 512KB to 4MB, Parity/ECC optional | ||||

| MMU | SV39, ITLB, DTLB | ||||

| Interrupt | CLINT, PLIC | ||||

| Debug | Debug module, supporting JTAG Trace module, supporting RISC-V standard E-Trace |

||||

| Bus Interfaces | 1. Memory Port: 128–bit AXI master interface 2. Peripheral Port: 128-bit AXI master interface 3. Front Port: 128-bit AXI slave interface |

||||

| Vector | supporting RVV1.0 | ||||