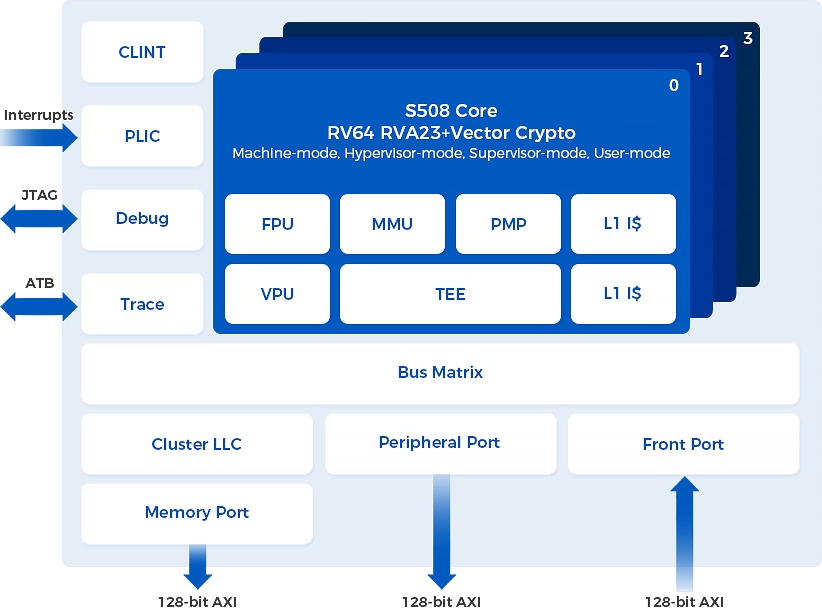

It adopts self-developed 9-stage pipeline,dual-issue and in-order architecture, and supports multicores and SMP. A core cluster can have up to 4 cores inside.

It supports RVA23-Profile to meet the requirements of Android platform and contains Hypervisor-mode to realize virtualization.

Tthe trusted execution environment is supported to meet the system security requirements.

The optional E-Trace/N-Trace for advanced debugging function is supported.

With the characteristics of high energy efficiency and extensive application fields. It can be applied to AIoT edge computing, network devices, baseband communication, etc

| Features | Description | ||||

| ISA | RVA23+Vector Crypto | ||||

| Multi-core | single core, dual core, 4 core option available | ||||

| Modes | Machine-mode, Hypervisor-mode, Supervisor-mode, User-mode | ||||

| Security | supporting ESWIN TEE solutions, with up to 64 PMP regions | ||||

| Crypto | supporting optional scalar, vector hardware encryption and decryption module | ||||

| Pipeline | 9-stage superscalar in-order pipeline, 2-way decode | ||||

| Branch Predictor | L0_BTB, BTB, IJTB, BHT, RAS, Loop Buffer | ||||

| L1 I$ | configurable sizes from 8KB to 64KB, ECC optional | ||||

| L1 D$ | configurable sizes from 8KB to 64KB, ECC optional | ||||

| Cluster LLC | configurable sizes from 256KB to 4MB, ECC optional | ||||

| MMU | SV39, ITLB, DTLB | ||||

| Interrupt | CLINT, PLIC | ||||

| Debug | Debug module, supporting JTAG Trace module, supporting RISC-V standard E-Trace/ N-Trace |

||||

| Bus Interface | 1. Memory Port: 128–bit AXI master interface 2. Peripheral Port: 128-bit AXI master interface 3. Front Port: 128-bit AXI slave interface |

||||

| Vector | supporting RVV1.0 | ||||