Based on S500, meets ASIL-B automotive safety certification.

It integrates self-developed 9-stage pipeline, dual-issue, in-order architecture.

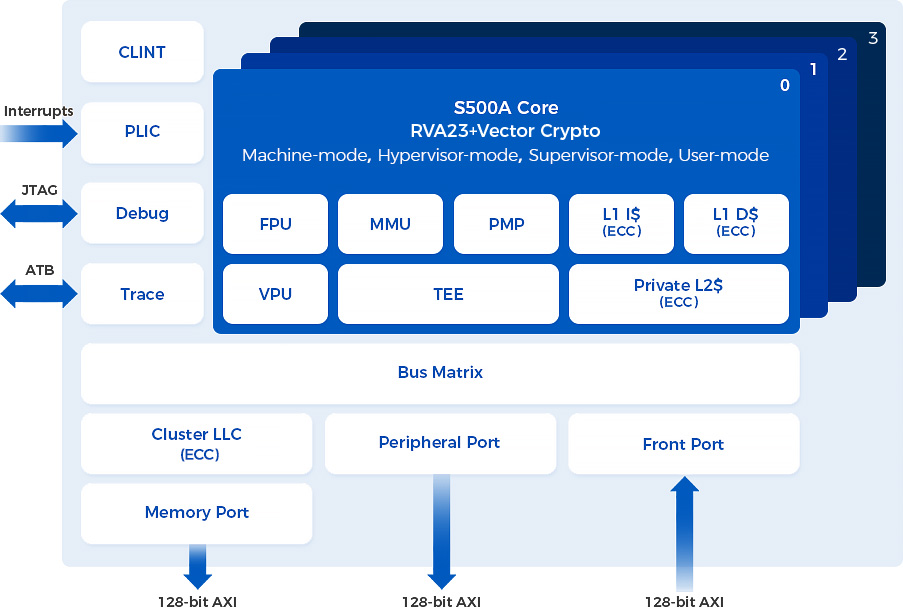

It supports SPM. A core cluster with up to 4 cores inside.

It supports RVA23-Profile to meet the requirements of Android platform and contains Hypervisor-mode to realize virtualization.

It also supports the trusted execution environment to meet the system security requirements.

Optional E-Trace/Ntrace for advanced debugging function is supported.

It supports ECC protection to meet hardware security requirements.

It is high energy-efficient application cores and can be used in broad applications, such as AIoT edge computing, network devices, baseband communication, automotive and etc.

| Features | Description | ||||

| ISA | RVA23+Vector Crypto | ||||

| Multi-core | Single-core, dual-core, quad-core options | ||||

| Modes | Machine-mode, Hypervisor-mode, Supervisor-mode, User-mode | ||||

| Security | Supports ESWIN TEE solution, with up to 64 PMP regions | ||||

| Crypto | Supports optional scalar, vector hardware encryption and decryption module | ||||

| Pipeline | 9-stage superscalar in-order pipeline, 2-way decode | ||||

| Branch Predictor | L0_BTB, BTB, IJTB,BHT, RAS, Loop Buffer | ||||

| L1 I$ | Size is configurable from 8KB to 64KB. ECC optional | ||||

| L1 D$ | Size is configurable from 8KB to 64KB. ECC optional | ||||

| Cluster LLC | Size is configurable from 256KB to 4MB. ECC optional | ||||

| MMU | SV39,ITLB,DTLB | ||||

| Interrupt | CLINT,PLIC | ||||

| Debug | Debug module: supports JTAG Trace module: supports RISC-V standard E-Trace/ N-Trace |

||||

| Bus Interface | 1.Memory Port: 128–bit AXI master interface 2.Peripheral Port: 128-bit AXI master interface 3.Front port : 128-bit AXI slave interface |

||||

| Vector Extension | Supports RVV1.0 | ||||

| CoreMark(CoreMarks/MHz) | 6.27 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 2.90 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号