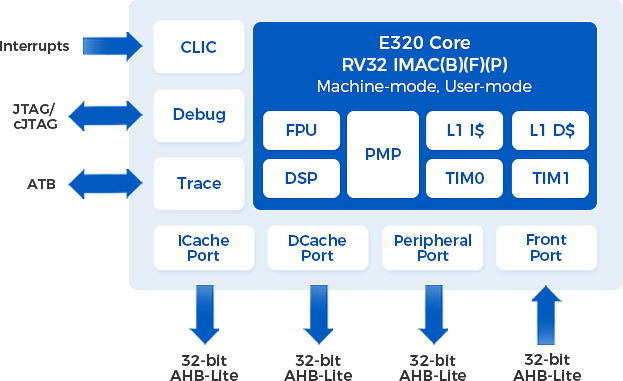

Besides RV32IMACB(F) instruction sets, it supports the complete set of RISC-V DSP extension v0.9.11, including 244 instructions of Zpn + Zbpbo + Zpsfoperand.

For advanced debugging, E320 has option to take RISC-V N-Trace for instruction trace.

| Features | Description | ||||

| ISA | RISC-V 32-bit IMAC(B)(F)(P)_Zicsr_Zifencei_Zicbom | ||||

| Modes | Machine-mode, User-mode | ||||

| Security | Supporting Smepmp, PMP Region can optional from 0 to 16 | ||||

| Pipeline | 3-stage pipeline | ||||

| TIM | TIM0 and TIM1, with configurable sizes from 0KB to 128MB | ||||

| L1 I$ | Size is configurable from 4KB to 128KB | ||||

| L1 D$ | Size is configurable from 4KB to 128KB | ||||

| Interrupt | CLIC interrupt controller, supports 496 interrupt requests and non-maskable interrupt(NMI) | ||||

| Debug | Debug module: supports JTAG/cJTAG Trace module: supports RISC-V N-Trace |

||||

| Bus Interface | 1.ICache Port: 32-bit AHB-Lite master interface 2. Dcache Port: 32-bit AHB-Lite master interface 3. Peripheral Port: 32-bit AHB-Lite master interface 4. Front Port: 32-bit AHB-Lite slave interface |

||||

| CoreMark(CoreMarks/MHz) | 4.45 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 1.74 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号