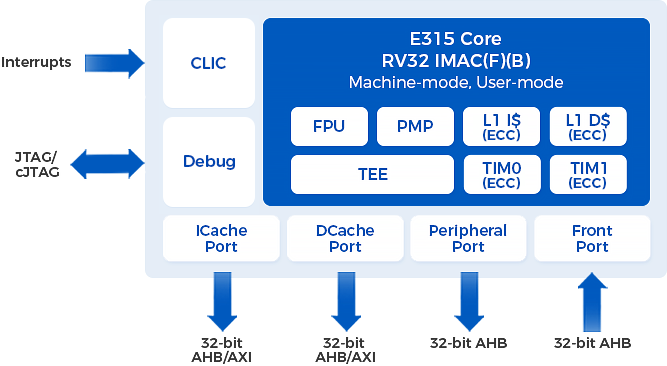

On top of E310, E315 has the optional features, such as RV32B bit operation extension, RV32F floating-point extension, and has L1 cache with Harvard interface and Zicbom cache operation extension.

Meanwhile, it can take either AXI bus or AHB bus for xCache (ICache or Dcache) external interfaces.

| Features | Description | ||||

| ISA | RISC-V 32-bit IMAC(F)(B)_Zicsr_Zifencei_Zicbom | ||||

| Modes | Machine-mode, User-mode | ||||

| Security | Supporting Smepmp, PMP Region is optional from 0 to 16 Supports PPMA (Programmable Physical Memory Attributes) check Optional ESWIN Trusted Execution Environment (TEE) solution with physical memory protection (PMP) regions up to 64 |

||||

| Pipeline | 3-stage pipeline | ||||

| TIM | TIM0 and TIM1, with configurable sizes from 0KB to 128MB,ECC optional | ||||

| L1 I$ | Size is configurable from 4KB to 128KB. Parity/ECC optional | ||||

| L1 D$ | Size is configurable from 4KB to 128KB. Parity/ECC optional | ||||

| Interrupt | CLIC interrupt controller, supports 112 interrupt requests and non-maskable interrupt(NMI) | ||||

| Debug | Debug module, supports JTAG/cJTAG | ||||

| Bus Interface | 1. ICache Port: 32-bit AHB/AXI master interface 2. DCache Port: 32-bit AHB/AXI master interface 3. The instruction cache interface and the data cache interface can be combined into one system interface: 32-bit AHB/AXI master interface 4. Peripheral Port:32-bit AHB master interface 5. Front port: 32-bit AHB slave interface, used for external access to TIMs |

||||

| CoreMark(CoreMarks/MHz) | 4.45 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 1.72 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号