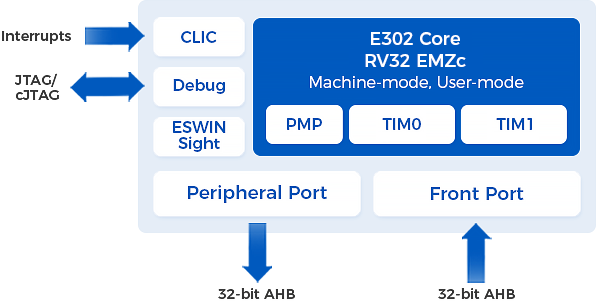

Supports the RISC-V latest Zc V1.0 compression instruction extension and Smepmp security extension. Compare to E301, E302 has better energy efficiency and higher code density.

Supports two optional Tightly-Integrated Memories (TIMs) which can be used to store instructions or data. And supports external host access TIMs through the front port.

To ease user RTL simulation debugging, it provides an ESWIN Sight function to let users easily probe the internal state, registers and events.

| Features | Description | ||||

| ISA | RISC-V 32-bit EMZc_Zicsr_Zifencei | ||||

| Modes | Machine-mode, User-mode | ||||

| Security | PMP Region can optional from 0 to 16 | ||||

| Pipeline | 3-stage pipeline | ||||

| TIM | TIM0 and TIM1, with configurable sizes from 0KB to 128MB | ||||

| Interrupt | CLIC interrupt controller, supports 112 interrupt requests and non-maskable interrupt(NMI) | ||||

| Debug | Debug module, supports JTAG/cJTAG | ||||

| Bus Interface | 1.Peripheral Port: 32-bit AHB master interface 2. Front port: 32-bit AHB slave interface, used for external access to TIM0 and TIM1 |

||||

| CoreMark(CoreMarks/MHz) | 3.25 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 1.47 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号