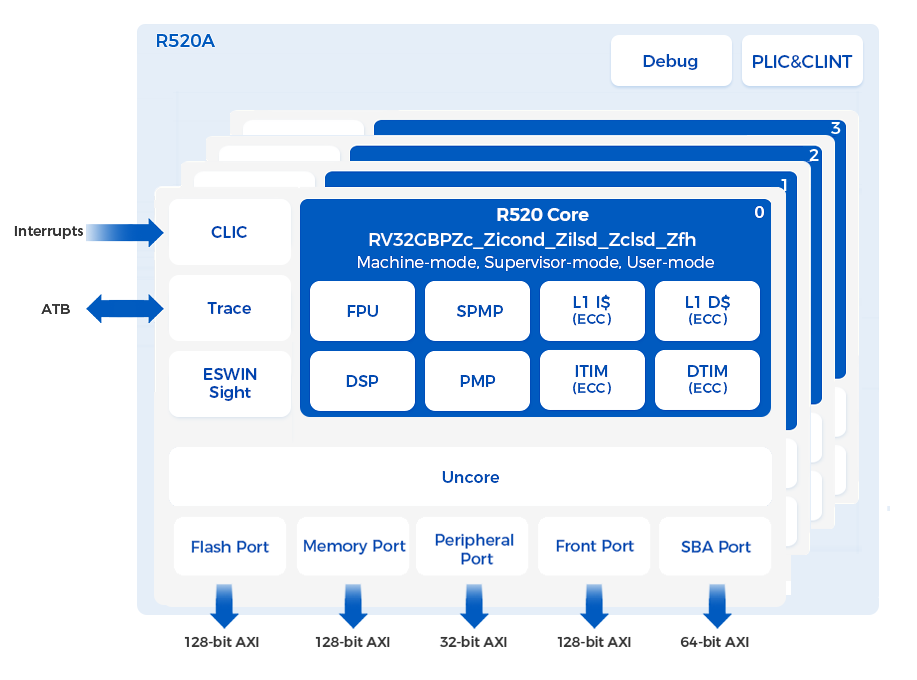

Support the RV32GCBP instruction set, including official extensions such as Zfh (semi precision floating-point), Zicobom (cache operation), Zicond (conditional execution), Zicsr (CSR read and write), Zience (fetch barrier), SmePMP (enhanced address protection), SPMP (supervised mode address protection), SBA (system mainline access), etc.

Support functions such as PPMA (Programmable Address Attribute Check), cache consistency feature Stack Monitor, ESWIN Sight (Internal Signal Insight), N-Trace (Instruction Flow Tracking), etc.

Supports Dual Core LockStep with Split/Lock modes. In Dual Core Lock mode, per two R500A cores in synchronized, enabling fault detection and reporting during system runtime, with error filtering and handling decided by the integrated environment; In Dual Core Split mode, the R500A core can decouple through configuration to independently execute different instruction sequences, improve processing performance, and match more application scenarios.

Supports multiple functional safety mechanisms: bus interface protection, SRAM interface protection, and non-safety module isolation.

It can run various real-time operating systems such as RTOS and μClinux, and is also compatible with Linux operating systems that support SPMP.

Suitable for designs with high requirements for interrupt processing speed, such as industrial control, medical device control, storage device control, modem, 5G communication, streaming media transmission, etc., especially suitable for in vehicle ECU/DCU and automotive grade IC design fields.

| Features | Description | ||||

| ISA | RV32GBP_Zicbom_Zicond_Zilsd_Zca_Zcb_Zcd_Zclsd_Zfh | ||||

| Pipeline | 6-stage superscalar in-order pipeline, with Branch Predictor | ||||

| Modes | Machine-mode, Supervisor-mode, User-mode | ||||

| Security | PMP region can reach up to 16, supporting PPMA SPMP region can reach up to 16 |

||||

| TIM | ITIM and DTIM, with configurable sizes from 0KB to 2MB, ECC optional | ||||

| DTIM | ITIM and DTIM, with configurable sizes from 0KB to 2MB, ECC optional | ||||

| L1 I$ | Configurable size (0KB-128KB), 2-way set-associative, 64-byte Cacheline, ECC optional | ||||

| L1 D$ | Configurable size (0KB-128KB), 4-way set-associative, 64-byte Cacheline, ECC optional | ||||

| FPU | Supports RISC-V Zfh half-precision, single-precision and double-precision floating-point | ||||

| DSP | Supports full RV32P | ||||

| Interrupt | Supports CLIC interrupt controller with up to 1008 fast interrupts per core Supports PLIC interrupt controller with up to 1024 external interrupt sources Supports recoverable non-maskable interrupt (NMI) |

||||

| Debug | Debug module: supports JTAG/cJTAG and SBA(System Bus Access Port) Trace module: supports RISC-V N-Trace |

||||

| 总线接口 | 1. Flash Port: 128-bit read-only AXI master interface 2.Memory Port:128-bit AXI master interface 3.Peripheral Port:32-bit AXI master interface 4.Front Port:128-bit AXI slave interface, used for external access to ITIM , DTIM and DCache |

||||

| CoreMark(CoreMarks/MHz) | 5.81 | ||||

| Dhrystone-Legal(DMIPS/MHz) | 2.83 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号