基于S500,满足ASIL-B功能安全标准。

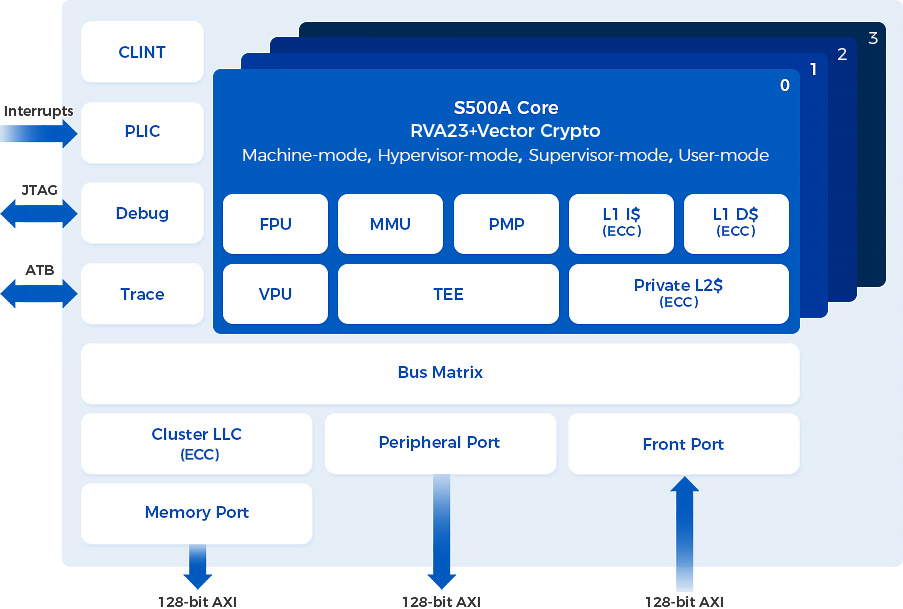

采用自研9级流水双发架构,支持最多4核,支持SMP;

支持RVA23-Profile,以满足Android的平台要求;

支持Hypervisor-mode,可实现虚拟化;

支持可信的执行环境、满足系统安全需求;

支持可选E-Trace/N-Trace的调试功能,便于功能调试;

支持ECC保护,满足硬件安全需求;

具有高能效、应用领域广泛的特点,可应用于移动终端、显示设备、AIoT边缘计算、网络设备、基带通信和车载等领域。

| 特性 | 描述 | ||||

| 指令集架构 | RVA23+Vector Crypto | ||||

| 多核 | 单核,双核,4核可选 | ||||

| 模式 | 支持机器模式(Machine-mode)、虚拟机管理模式(Hypervisor-mode)、监督模式(Supervisor-mode)、用户模式(User-mode) | ||||

| 安全 | 支持ESWIN可信执行环境(TEE)方案,物理内存保护(PMP)区域最高可达64个 | ||||

| Crypto | 支持可选标量、向量硬件加解密模块 | ||||

| 流水线 | 9级超标量顺序流水线,2路解码 | ||||

| 分支预测器 | L0_BTB, BTB, IJTB,BHT, RAS, Loop Buffer | ||||

| L1 指令缓存(L1 I$) | 大小可选配(8KB,16KB,32KB 或 64KB), ECC 可选 | ||||

| L1 数据缓存(L1 D$) | 大小可选配(8KB,16KB,32KB 或 64KB), ECC 可选 | ||||

| 共享最后一级缓存(Cluster LLC) | 大小可选配(256KB-4MB),ECC可选 | ||||

| 内存管理单元 | SV39,ITLB,DTLB | ||||

| 中断 | CLINT,PLIC | ||||

| 调试跟踪 | 调试模块(Debug module)支持JTAG 跟踪模块(Trace module)支持RISC-V标准的E-Trace/ N-Trace |

||||

| 总线接口 | 1.内存接口(Memory Port):128位AXI主接口 2.外设接口(Peripheral Port):128位AXI主接口 3.前置接口(Front port) :128位AXI从接口 |

||||

| 矢量扩展(Vector) | 支持RVV1.0 | ||||

| CoreMark(CoreMarks/MHz) | 6.27 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 2.90 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号