支持RV32GCBP指令集,支持Zfh(半精度浮点)、Zicbom(缓存操作)、Zicond(条件执行)、Zicsr(CSR读写)、Zifence(取指屏障)、SmePMP(加强版地址保护)、SPMP(监督模式地址保护)、SBA(系统总线访问)等官方扩展;

支持PPMA(可编程地址属性检查)、Stack Monitor(栈监控)、ESWIN Sight(内部信号洞察)、N-Trace(指令流跟踪)等功能;

支持缓存一致性功能,允许外部设备通过Front Port访问DCache,以满足部分场景下对缓存一致性的功能需求;

支持多种功能安全机制:寄存器奇偶校验、总线接口保护、SRAM接口保护和非安全模块隔离;

可运行各类实时操作系统,例如RTOS、μClinux等,还兼容支持SPMP的Linux操作系统;

适用于对中断处理速度有高要求的设计中,例如工业控制、医疗设备控制、存储设备控制、Modem、5G通信、流媒体传输等,特别适用于车载ECU/DCU、车规级IC设计领域。

| 特性 | 描述 | ||||

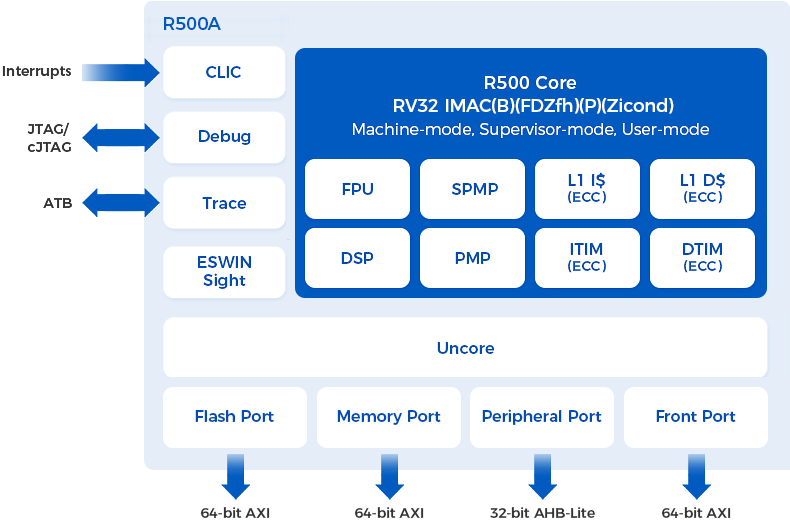

| 指令集架构 | RISC-V 32位 IMAC(B)(FDZfh)(P)_Zicsr_Zifencei_Zicbom_(Zicond) | ||||

| 流水线 | 6级超标量顺序双发射流水线,带分支预测器(Branch Predictor) | ||||

| 模式 | 机器模式(Machine-mode)、监督模式(Supervisor-mode)、用户模式(User-mode) | ||||

| 安全 | PMP保护区域最高可达16个,SPMP保护区域最高可达16个; 支持 PPMA(Programmable Physical Memory Attributes) 检查 |

||||

| 指令紧密集成存储(ITIM) | 0-16MB大小可配,ECC 可选 | ||||

| 数据紧密集成存储(DTIM) | 0-16MB大小可配,ECC 可选 | ||||

| L1 指令缓存(L1 I$) | 0-128KB大小可配置, 两路组相连32B Cacheline,ECC 可选 | ||||

| L1 数据缓存(L1 D$) | 0-128KB大小可配置, 四路组相连32B Cacheline,ECC 可选 | ||||

| 中断 | 支持CLIC 中断控制器,至多支持1008个快速中断 支持可恢复的NMI不可屏蔽中断 |

||||

| 浮点运算单元 (FPU) | 支持双精度、单精度,以及RISC-V Zfh半精度浮点拓展 | ||||

| 数字信号处理单元 (DSP) | 支持单指令多数据(SIMD)指令,支持全量的RISC-V RV32P拓展 | ||||

| 调试跟踪 | 调试模块(Debug module)支持JTAG/cJTAG,支持SBA(System Bus Access); 跟踪模块(Trace module)支持RISC-V N-Trace |

||||

| 总线接口 | 1. 闪存接口(Flash Port):64位只读AXI主接口 2.内存接口(Memory Port):64位AXI主接口 3.外设接口(Peripheral Port):32位AHB-Lite主接口 4.前置接口(Front Port) :64位 AXI从接口,用于从外部访问 ITIM 、 DTIM和DCache |

||||

| CoreMark(CoreMarks/MHz) | 5.79 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 2.55 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号