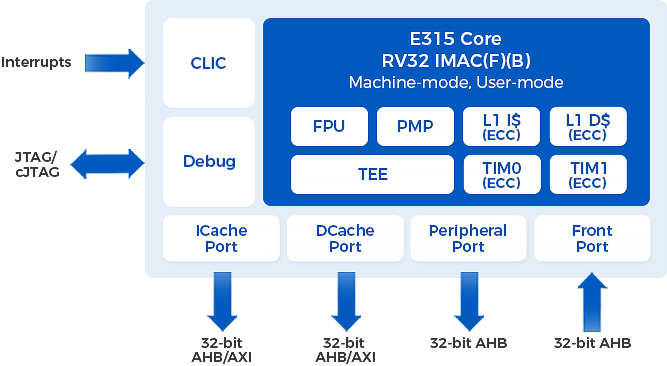

相比E310,增加可选配RV32B位操作扩展和RV32F单精度浮点扩展,增加哈佛接口的L1缓存和Zicbom缓存操作扩展;

可选外部主机接口AXI/AHB。

| 特性 | 描述 | ||||

| 指令集架构 | RISC-V32位IMAC(F)(B)_Zicsr_Zifencei _Zicbom | ||||

| 模式 | 机器模式(Machine-mode)、用户模式(User-mode) | ||||

| 安全 | 支持Smepmp;可选0-16个物理内存保护(PMP)区域 支持 PPMA(Programmable Physical Memory Attributes) 检查 可选ESWIN可信执行环境(TEE)方案,物理内存保护(PMP) 区域最高可达64个 |

||||

| 流水线 | 3级流水线 | ||||

| 处理器内存储 | TIM0 和 TIM1,大小均可配置(0KB-128MB),ECC 可选 | ||||

| L1指令缓存(L1 I$) | 大小可配置(4KB-128KB),Parity/ECC可选 | ||||

| L1数据缓存(L1 D$) | 大小可配置(4KB-128KB),Parity/ECC可选 | ||||

| 中断 | CLIC中断控制器,支持高达112个中断请求,支持不可屏蔽中断(NMI) | ||||

| 调试 | 调试模块(Debug module)支持JTAG/cJTAG | ||||

| 总线接口 | 1. 指令缓存接口(ICache Port):32位AHB/AXI主接口 2. 数据缓存接口(DCache Port):32位AHB/AXI主接口 3. 指令缓存接口和数据缓存接口可合为一个系统接口(System Port): 32位AHB/AXI主接口 4. 外设接口(Peripheral Port):32位AHB主接口 5. 前置接口(Front port): 32位AHB从接口,用于从外部访问TIM |

||||

| CoreMark(CoreMarks/MHz) | 4.45 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 1.72 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号