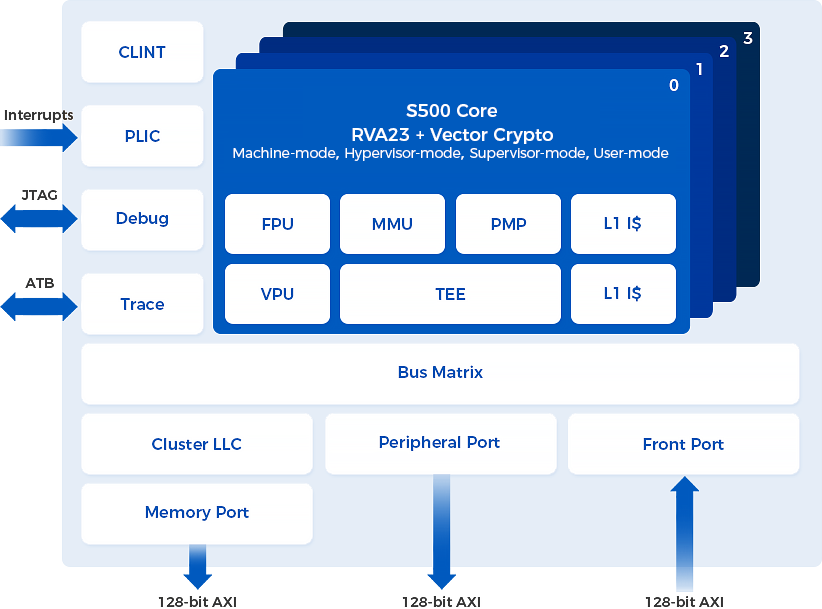

자체 개발한 9 스테이지 파이프라인 듀얼 이슈 아키텍처를 채택하여 최대 쿼드코어를 지원하고 SMP 를 지원합니다.

RVA23-Profile 을 지원하여 Android플랫폼 요구 사항을 충족시킬 수 있습니다.

Hypervisor-mode 를 지원하며 가상화를 실현할 수 있습니다.

신뢰할 수 있는 실행 환경을 지원하며 시스템 보안 요구 사항을 충족합니다.

기능 디버깅을 위한 옵션 E-Trace/N-Trace의 디버깅 기능을 지원합니다.

에너지 효율이 높고 넓은 영역에 적용할 수 있는 특징을 가지고 있으며 모바일 단말, 디스플레이 장치, AIoT 엣지 컴퓨팅, 네트워크 장비, 베이스밴드 통신 등 분야에 적용할 수 있습니다.

| 특성 | 설명 | ||||

| 명령어 집합 아키텍처 | RVA23+Vector Crypto | ||||

| 멀티 코어 | 단일 코어,듀얼 코어,쿼드 코어 옵션 | ||||

| 모드 | 머신 모드(Machine-mode),하이퍼바이저 모드(Hypervisor-mode), 슈퍼바이저 모드(Supervisor-mode), 유저 모드(User-mode)지원 | ||||

| 보안 | ESWIN신뢰 실행 환경(TEE)솔루션 지원, 물리 메모리 보호(PMP) 구역 최대 64개까지 가능 | ||||

| Crypto | 스칼라, 벡터 하드웨어 암호화 및 복호화 모듈 옵션 지원 | ||||

| 파이프라인 | 9스테이지 슈퍼스칼라 순차적 파이프라인,2채널 디코드 | ||||

| 분기 예측기 | L0_BTB, BTB, IJTB,BHT, RAS, Loop Buffer | ||||

| L1 명령어 캐시(L1 I$) | 사이즈 설정 가능(8KB,16KB,32KB 또는 64KB) | ||||

| L1 데이터 캐시(L1 D$) | 사이즈 설정 가능(8KB,16KB,32KB 또는 64KB) | ||||

| 종단 레벨 캐시 공유 (Cluster LLC) | 사이즈 설정 가능(256KB-4MB) | ||||

| 메모리관리장치 | SV39,ITLB,DTLB | ||||

| 인터럽트 | CLINT,PLIC | ||||

| 디버그 추적 | 디버그 모듈(Debug module)JTAG지원 추적 모듈(Trace module) RISC-V 표준의 E-Trace/N-Trace 지원 |

||||

| 버스 포트 | 1. 메모리 포트(Memory Port):128 비트 AXI 마스터 포트 2.주변 장치 포트(Peripheral Port):128 비트 AXI 마스터 포트 3.프론트 포트(Front port) :128 비트 AXI 슬레이브 포트 |

||||

| 벡터 확장(Vector) | RVV1.0 지원 | ||||

| CoreMark(CoreMarks/MHz) | 6.27 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 2.90 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号