RV32GCBP 명령어 집합 지원, Zfh(반정밀도부동소수점), Zicbom(캐시작업), Zicond(조건실행), Zicsr(CSR 읽기및쓰기), Zifence(명령어인출장애), SmePMP(강화된 주소 보호), SPMP(슈퍼바이저모드 주소 보호), SBA(시스템버스액세스)등 공식 확장을 지원합니다.

PPMA(프로그래밍 가능 주소 속성 검사), 캐시 일관성 기능, Stack Monitor(스택모니터), ESWIN Sight(내부신호통찰), N-Trace(명령어흐름추적)등 기능을 지원합니다.

Dual-Core LockStep(듀얼코어 록스텝)을 지원하며 Split/Lock 두 개 모드를 갖추고 있습니다. Dual-Core Lock모드에서는두 개의 R500A 코어마다 동기화되어 실행되며 시스템이 실행되는 동안 고장 감지 및 보고가 가능하고 통합 환경에 의해 오류 필터링 및 처리가 결정됩니다.Dual-Core Split 모드에서는 R500A 코어를 분리 설정하여 서로 다른 명령어 시퀀스를 독립적으로 실행할 수 있어 처리성능을 향상시키며 더 많은 응용처에 대응할 수 있습니다.

다양한 기능 안전 메커니즘을 지원합니다:버스 포트 보호, SRAM 포트 보호 및 비안전 모듈 격리.

RTOS、μClinux등과 같은 다양한 실시간 운영 체제를 실행 가능하며 SPMP를 지원하는 Linux운영체제와 호환됩니다.

산업 제어, 의료 장비 제어, 저장 장치 제어, Modem, 5G 통신, 스트리밍 미디어전송 등 높은 인터럽트 처리 속도를 요하는 설계에 적합하며 특히 차량용ECU/DCU, 전장급 IC 설계 분야에 적합합니다.

| 특성 | 설명 | ||||

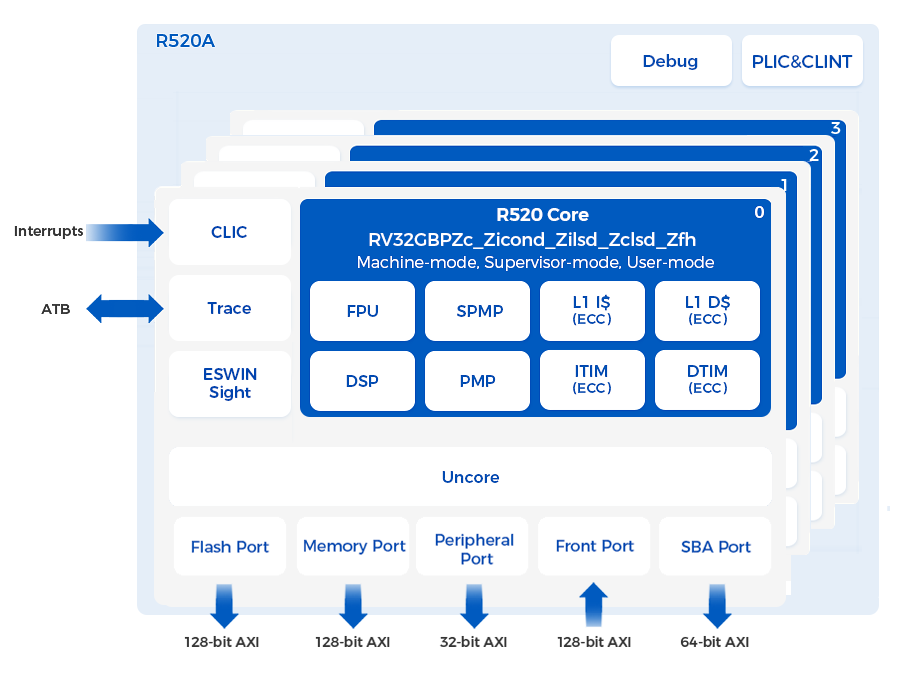

| 명령어 집합 아키텍처 | RV32GBP_Zicbom_Zicond_Zilsd_Zca_Zcb_Zcd_Zclsd_Zfh | ||||

| 파이프라인 | 6스테이지 슈퍼스칼라 순차 듀얼 이슈 파이프라인,분기 예측기(Branch Predictor)포함 | ||||

| 모드 | 머신모드(Machine-mode), 슈퍼바이저모드(Supervisor-mode), 유저모드(User-mode) | ||||

| 보안 | PMP보호 구역 최대 16개, SPMP보호 구역 최대 16개까지 가능 PPMA(Programmable Physical Memory Attributes) 검사 지원 |

||||

| 명령어 밀착 통합 메모리(ITIM) | 0-2MB사이즈 설정 가능,ECC 옵션 | ||||

| 데이터 밀착 통합 메모리(DTIM) | 0-2MB사이즈 설정 가능,ECC 옵션 | ||||

| L1 명령어 캐시(L1 I$) | 0-128KB사이즈 설정 가능, 2-way 세트 연관64B Cacheline,ECC 옵션 | ||||

| L1 데이터 캐시(L1 D$) | 0-128KB사이즈 설정 가능, 4-way 세트 연관64B Cacheline,ECC 옵션 | ||||

| 부동 소수점 장치 (FPU) | 배정밀도,단정밀도 및 RISC-V Zfh 반 정밀도 부동 소수점 확장 지원 | ||||

| 디지털 신호 처리 장치 (DSP) | 전체 RISC-V RV32P 확장 지원 | ||||

| 인터럽트 | CLIC 인터럽트 컨트롤러 지원,코어당 최대 1,008 개 빠른 인터럽트 요청 지원 CLIC 인터럽트 컨트롤러 지원,최대1,024개 외부 인터럽트 소스 지원, 회복 가능한 NMI 마스크 불가능 인터럽트 지원 |

||||

| 디버그 추적 | 디버그 모듈(Debug module)JTAG/cJTAG, SBA(System Bus AccessPort)지원 추적 모듈(Trace module)RISC-V N-Trace지원 |

||||

| 버스 포트 | 1. 플래시 포트(Flash Port): 128비트 읽기 전용 AXI 마스터 포트 2. 메모리 포트(Memory Port):128비트 AXI 마스터 포트 3. 주변 장치 포트(Peripheral Port):32비트 AXI 마스터 포트 4.프론트 포트(Front Port):128비트 AXI 슬레이브 포트, ITIM, DTIM 에 대한 외부 액세스용 5. Debug SBA 포트(SBA Port): 64비트 AXI 마스터 포트, 외부시스템 메모리에 대한 Debug SBA 액세스용 |

||||

| CoreMark(CoreMarks/MHz) | 5.81 | ||||

| Dhrystone-Legal(DMIPS/MHz) | 2.83 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号