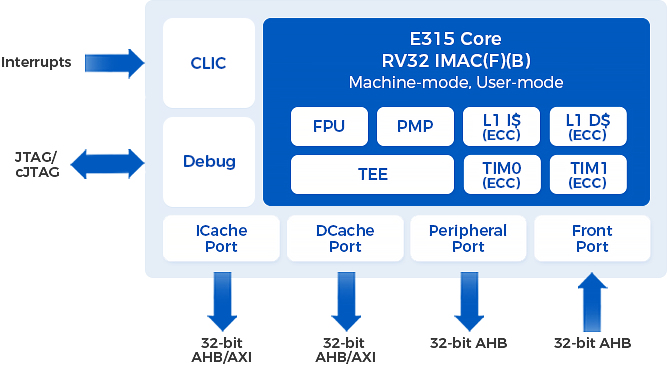

E310대비 옵션 RV32B 비트 작업 확장, RV32F 단정밀도 부동 소수점 확장, Harvard architecture의 L1 캐시 및 Zicbom 캐시 작업 확장을 추가하였습니다.

외부 호스트 포트 AXI/AHB옵션을제공합니다.

| 특성 | 설명 | ||||

| 명령어 집합 아키텍처 | RISC-V 32-bit IMAC(F)(B)_Zicsr_Zifencei_Zicbom | ||||

| 모드 | 머신모드(Machine-mode),유저모드(User-mode) | ||||

| 보안 | Smepmp지원, 0-16개 물리 메모리 보호(PMP)구역 옵션 PPMA(Programmable Physical Memory Attributes) 검사 지원 ESWIN신뢰 실행 환경(TEE)솔루션 옵션, 물리 메모리 보호(PMP) 구역 최대 64 개까지 가능 |

||||

| 파이프라인 | 3스테이지 파이프라인 | ||||

| 프로세서 메모리 | TIM0 및 TIM1,사이즈 설정 가능(0KB-128MB), ECC 옵션 | ||||

| L1 명령어캐시(L1 I$) | 사이즈 설정 가능(4KB-128KB), Parity/ECC 옵션 | ||||

| L1 데이터캐시(L1 D$) | 사이즈 설정 가능(4KB-128KB), Parity/ECC 옵션 | ||||

| 인터럽트 | CLIC 인터럽트 컨트롤러, 112 개 인터럽트 요청 지원, 마스크 불가능인터럽트(NMI) 지원 | ||||

| 디버그 | 디버그 모듈(Debug module)JTAG/cJTAG 지원 | ||||

| 버스 포트 | 1.명령어 캐시 포트(ICache Port):32비트 AHB/AXI 마스터 포트 2.데이터 캐시 포트(DCache Port):32 비트 AHB/AXI 마스터 포트 3.명령어 캐시 포트 및 데이터 캐시포트는 하나의 시스템포트(System Port)로 결합 가능: 32비트 AHB/AXI마스터 포트 4.주변 장치 포트(Peripheral Port):32비트 AHB 마스터 포트 5.프론트 포트(Front port): 32비트 AHB슬레이브 포트,TIM에 대한 외부 액세스용 |

||||

| CoreMark(CoreMarks/MHz) | 4.45 | ||||

| Dhrystone-Legal(DMIPS/MHz) | 1.72 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号