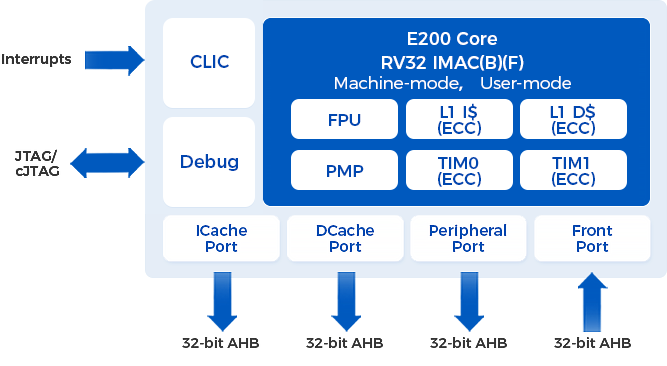

本製品は、組込み向けの軽量マイコンアプリケーションに特化して設計されており、性能向上のために以下の機能が追加されています:L1キャッシュの搭載、B拡張への対応、F拡張への対応、Zicbomへの対応、Smepmp(セキュリティ拡張)への対応。

| 特徴 | 説明 | ||||

| 命令セットアーキテクチャ | RISC-V 32-bit IMAC(B)(F) に対応 | ||||

| 動作モード | マシンモード、ユーザモードに対応 | ||||

| セキュリティ | Smepmp に対応、最大 0~16 個の物理メモリ保護領域(PMP)を設定可能 PPMA(Programmable Physical Memory Attributes)チェックに対応 |

||||

| パイプライン構成 | 2段パイプライン | ||||

| プロセッサ内部メモリ | TIM0 および TIM1 を搭載、サイズは 0KB~128MB で設定可能、ECC(誤り訂正符号)オプションあり | ||||

| L1 命令キャッシュ(L1 I$) | 容量は 4KB~128KB で設定可能、Parity / ECC オプションあり | ||||

| L1 データキャッシュ(L1 D$) | 容量は 4KB~128KB で設定可能、Parity / ECC オプションあり | ||||

| 割り込み制御 | CLIC割り込み制御装置に対応、最大112個の割り込み要求をサポート、ノンマスカブル割り込み(NMI)にも対応 | ||||

| デバッグ機能 | デバッグモジュール(Debug Module)は JTAG / cJTAG に対応 | ||||

| バスインタフェース | 1. 命令キャッシュインターフェース(ICache Port):32ビット AHB マスターインターフェース 2. データキャッシュインターフェース(DCache Port):32ビット AHB マスターインターフェース 3. 命令キャッシュとデータキャッシュを統合したシステムポート(System Port):32ビット AHB マスターインターフェース 4. ペリフェラルポート(Peripheral Port):32ビット AHB マスターインターフェース 5. フロントポート(Front Port):32ビット AHB スレーブインターフェース,外部から TIM にアクセス可能 |

||||

| CoreMark (CoreMarks/MHz) | 4.65 | ||||

| Dhrystone-Legal (DMIPS/MHz) | 1.90 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号