エッジコンピューティング、スマートテレビ、セットトップボックス、パソコン、モバイル端末などのさまざまなインテリジェントコンピューティング分野に適しています。

| 特徴 | 説明 | ||||

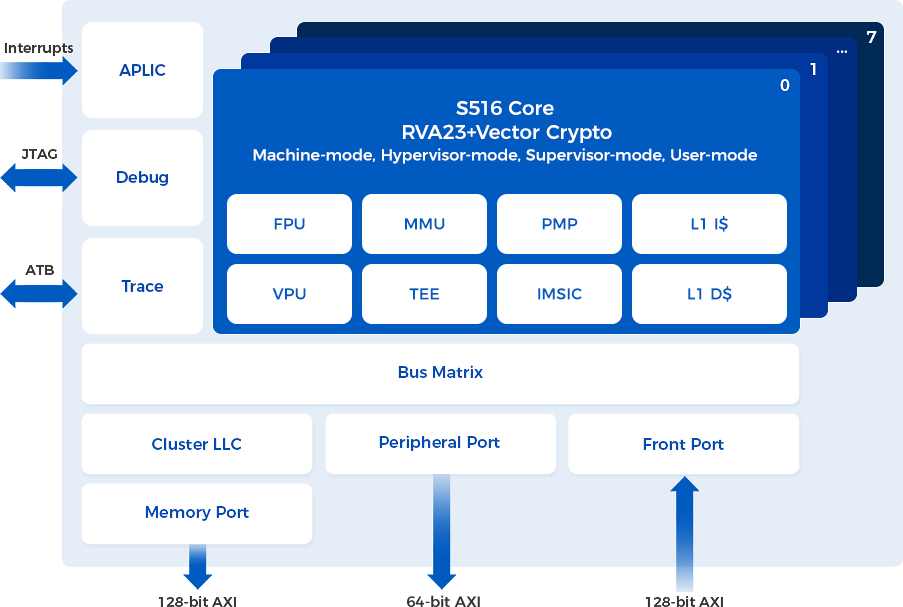

| 命令セットアーキテクチャ | RVA23+Vector Crypto に対応 | ||||

| マルチコア | 単一クラスタで最大8コアまで対応 | ||||

| 動作モード | マシンモード(Machine-mode)、ハイパーバイザモード(Hypervisor-mode)、スーパーバイザモード(Supervisor-mode)、ユーザモード(User-mode) | ||||

| セキュリティ | ESWINの信頼実行環境(TEE)ソリューションに対応、物理メモリ保護(PMP)最大64領域まで対応 | ||||

| 暗号処理 | スカラおよびベクトル型のハードウェア暗号/復号モジュール(オプション)に対応 | ||||

| ベクトル拡張 | RVV1.0 に対応、ベクトル幅は 128ビット/256ビット/512ビット/1024ビット から選択可能 | ||||

| 仮想化 | 仮想化対応(IOMMU+AIA) | ||||

| パイプライン | 8段スーパースカラ順序実行パイプライン、2命令同時デコード | ||||

| 分岐予測器 | L0_BTB、IJTB、NN-Predictor、RAS、ループバッファ(Loop Buffer)に対応 | ||||

| プリフェッチ機能 | 命令およびデータのプリフェッチ機能に対応 | ||||

| アーキテクチャの特長 | 命令融合、write streaming モード、一部アウトオブオーダー実行?に対応ンあり | ||||

| L1命令キャッシュ(L1 I$) | 容量選択可能(8KB、16KB、32KB、64KB)、ECC(誤り訂正)オプショ | ||||

| L1データキャッシュ(L1 D$) | 容量選択可能(8KB、16KB、32KB、64KB)、ECC(誤り訂正)オプションあり | ||||

| クラスタ共有最終キャッシュ(LLC) | 容量選択可能(256KB〜4MB)、ECC(誤り訂正)オプションあり | ||||

| メモリ管理ユニット(MMU) | SV39/SV48、ITLB、DTLB に対応。 ページテーブルエントリ(PTE)のハードウェア自己修正もサポート |

||||

| 割り込み制御 | APLIC(AIA+PLIC)に対応 | ||||

| デバッグ/トレース機能 | デバッグモジュール:JTAG対応 トレースモジュール:RISC-V標準のE-Trace/N-Traceに対応 |

||||

| バスインタフェース | 1. メモリポート:128ビット AXI マスターインターフェース 2. ペリフェラルポート:64ビット AXI マスターインターフェース 3. フロントポート:128ビット AXI スレーブインターフェース |

||||

京公网安备 11030102011303号

京公网安备 11030102011303号