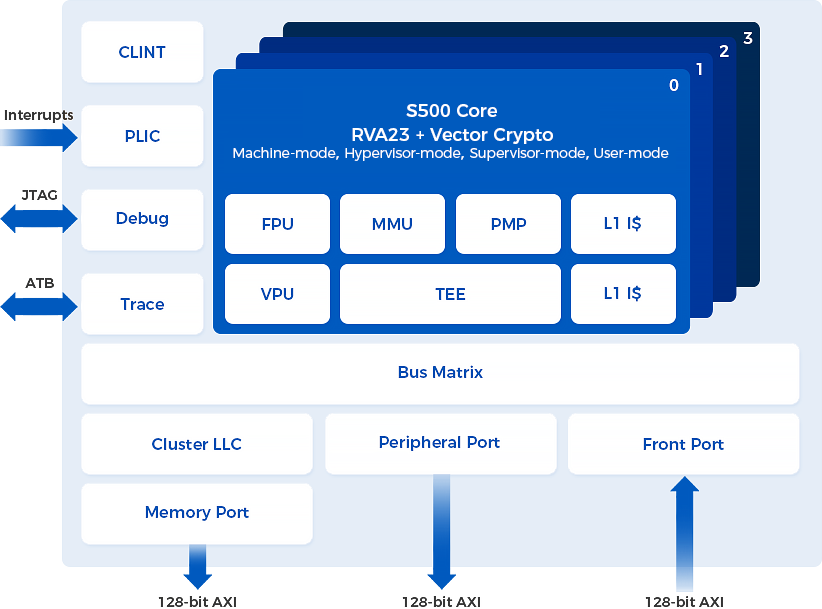

自社開発の9段パイプライン・デュアルイシューアーキテクチャを採用し、最大4コア構成およびSMP(対称型マルチプロセッシング)に対応。

Androidプラットフォームの要件を満たすため、RVA23プロファイルに準拠しています。

Hypervisorモードに対応しており、仮想化の実現が可能です。

信頼できる実行環境に対応し、システムのセキュリティ要件を満たします。

オプションでE-Trace/N-Traceによるデバッグ機能にも対応しており、機能のデバッグを効率的に行えます。

高いエネルギー効率と広い応用範囲を備えており、モバイル端末、ディスプレイ機器、AIoTエッジコンピューティング、ネットワーク機器、ベースバンド通信など、さまざまな分野で活用できます。

| 特徴 | 説明 | ||||

| 命令セットアーキテクチャ | RVA23+Vector Crypto に対応 | ||||

| マルチコア | シングルコア、デュアルコア、クアッドコア(4コア)から選択可能 | ||||

| 動作モード | マシンモード(Machine-mode)、ハイパーバイザモード(Hypervisor-mode)、スーパーバイザモード(Supervisor-mode)、ユーザモード(User-mode)に対応 | ||||

| セキュリティ | ESWINの信頼実行環境(TEE)ソリューションに対応、物理メモリ保護(PMP)は最大64領域までサポート | ||||

| 暗号処理 | 選択可能なスカラ及びベクトル暗号化・復号化ハードウェアモジュールに対応 | ||||

| パイプライン | 9段のスーパースカラ順序実行パイプライン、2命令同時デコード | ||||

| 分岐予測器 | L0_BTB、BTB、IJTB、BHT、RAS、Loop Bufferループバッファに対応 | ||||

| L1命令キャッシュ(I$) | 容量選択可能(8KB、16KB、32KB、64KB) | ||||

| L1データキャッシュ(D$) | 容量選択可能(8KB、16KB、32KB、64KB) | ||||

| クラスタ共有最終キャッシュ(LLC) | 容量選択可能(256KB〜4MB) | ||||

| メモリ管理ユニット(MMU) | SV39、ITLB、DTLB をサポート | ||||

| 割り込み | CLINT、PLIC に対応 | ||||

| デバッグ/トレース | デバッグモジュール:JTAG対応 トレースモジュール:RISC-V標準のE-Trace/N-Trace対応 |

||||

| バスインタフェース | 1. メモリポート:128ビットAXIマスターインターフェース 2. ペリフェラルポート:128ビットAXIマスターインターフェース 3. フロントポート:128ビットAXIスレーブインターフェース |

||||

| ベクトル拡張 | RVV1.0 に対応 | ||||

| CoreMark(CoreMarks/MHz) | 6.27 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 2.90 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号