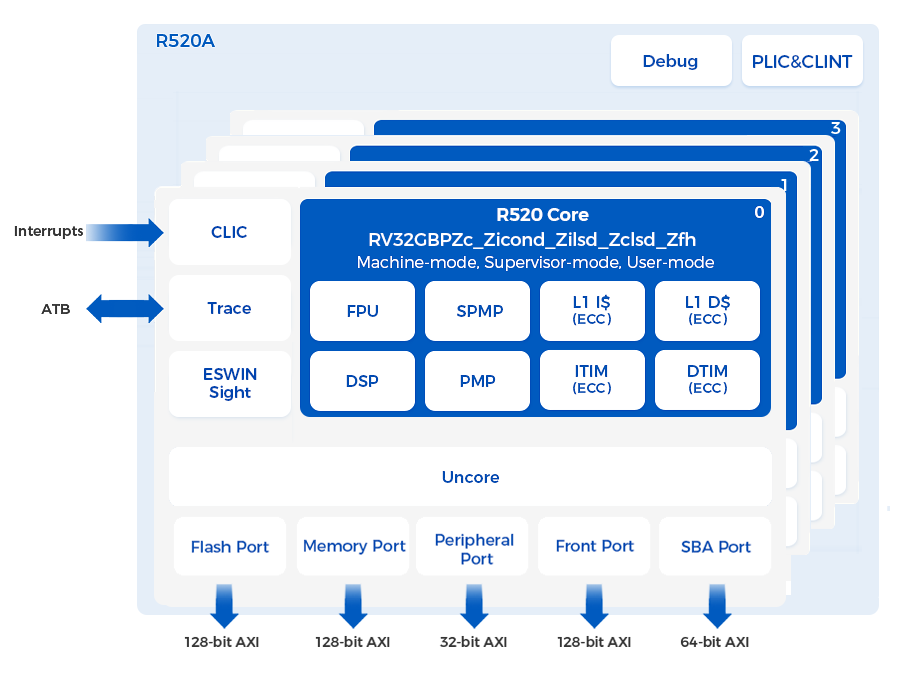

本製品は RV32GCBP命令セットに対応し、以下のRISC-V公式拡張機能をサポートします。 Zfh(半精度浮動小数点演算)、Zicbom(キャッシュ操作)、Zicond(条件付き実行)、Zicsr(CSRの読み書き)、Zifence(命令フェンス)、SmePMP(強化型物理メモリ保護)、SPMP(スーパーバイザーモードにおけるメモリ保護)、SBA(システムバスアクセス)。

PPMA(プログラマブルアドレス属性チェック)、キャッシュコヒーレンシ(キャッシュ一貫性)機能、Stack Monitor(スタックモニタリング)、ESWIN Sight(内部信号の可視化)、N-Trace(命令フローのトレース)などの機能をサポートしています。

本製品はDual-Core LockStep(デュアルコア・ロックステップ)をサポートしており、「Split(スプリット)」モードと「Lock(ロック)」モードの2種類の動作モードを備えています。 Dual-Core Lockモードでは、各2つのR500Aコアが完全に同期して動作し、システム稼働中に故障の検出およびレポートを行うことが可能です。エラーのフィルタリングおよび処理は、統合された環境(統合開発環境や安全管理機構)によって決定されます。一方、Dual-Core Splitモードでは、R500Aコアは設定によってデカップリングされ、異なる命令列を独立して実行することができるため、処理性能が向上し、より多様なアプリケーションシナリオに対応可能です。

各種の機能安全メカニズムをサポートしており、バスインタフェース保護、SRAMインタフェース保護、非セーフティモジュールとの分離などに対応しています。

各種のRTOSやμClinuxなどのリアルタイムオペレーティングシステムの実行が可能であり、SPMPに対応したLinuxオペレーティングシステムとの互換性・サポートも備えています。

本製品は、割り込み処理速度に対して高い要求がある設計に適しており、産業用制御、医療機器制御、ストレージ機器制御、モデム、5G通信、ストリーミング伝送などの分野に幅広く応用されています。特に、車載ECU/DCUや車載グレードのIC設計分野において、高い適用性を有しています。

| 特徴 | 説明 | ||||

| 命令セットアーキテクチャ | RV32 IMAC(B)(FDZfh)(P)_Zicsr_Zifencei_Zicbom_(Zicond)_Zilsd | ||||

| パイプライン | 6段のスーパースカラ順序型デュアルイシュー(Dual Issue)パイプライン 、分岐予測器付き | ||||

| 動作モード | マシンモード(Machine-mode)、スーパーバイザーモード(Supervisor-mode)、ユーザーモード(User-mode) | ||||

| セキュリティ | PMP保護領域:最大16個、SPMP保護領域:最大16個;PPMAチェックをサポート | ||||

| 命令密結合メモリ (ITIM) | 0〜2MBまで構成可能、ECCオプションあり | ||||

| データ密結合メモリ (DTIM) | 0〜2MBまで構成可能、ECCオプションあり | ||||

| L1命令キャッシュ(L1 I$) | 0〜128KBまで構成可能、2ウェイ・セットアソシアティブ、64バイトのキャッシュライン構成、ECC対応はオプション | ||||

| L1データキャッシュ(L1 D$) | 0〜128KBまで構成可能、4ウェイ・セットアソシアティブ、64バイトのキャッシュライン構成、ECC対応はオプション | ||||

| 浮動小数点演算ユニット(FPU) | 倍精度・単精度・RISC-V Zfh(半精度浮動小数点拡張)をサポート | ||||

| デジタル信号処理ユニット(DSP) | RISC-V RV32P拡張をフルサポート | ||||

| 割り込み機能 | CLIC割り込みコントローラ対応:各コア最大1008個の高速割り込みに対応 PLIC割り込みコントローラ対応:最大1024個の外部割り込みに対応 リカバリ可能なノンマスカブル割り込み(NMI)に対応 |

||||

| デバッグ・トレース | デバッグモジュール:JTAG/cJTAG、SBA(System Bus Access Port)対応 トレースモジュール:RISC-V N-Trace対応 |

||||

| バスインタフェース | 1.フラッシュポート(Flash Port):128ビットの読み取り専用AXIマスタインタフェース 2.メモリポート(Memory Port):128ビットAXIマスタインタフェース 3.ペリフェラルポート(Peripheral Port):32ビットAXIマスタインタフェース 4.フロントポート(Front Port):128ビットAXIスレーブインタフェース、外部ホストによるITIMおよびDTIMにアクセス用 5.デバッグSBAポート(SBA Port):64ビットAXIマスタインタフェース、Debug SBAによる外部システムメモリにアクセス用 |

||||

| CoreMark(CoreMarks/MHz) | 5.81 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 2.83 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号