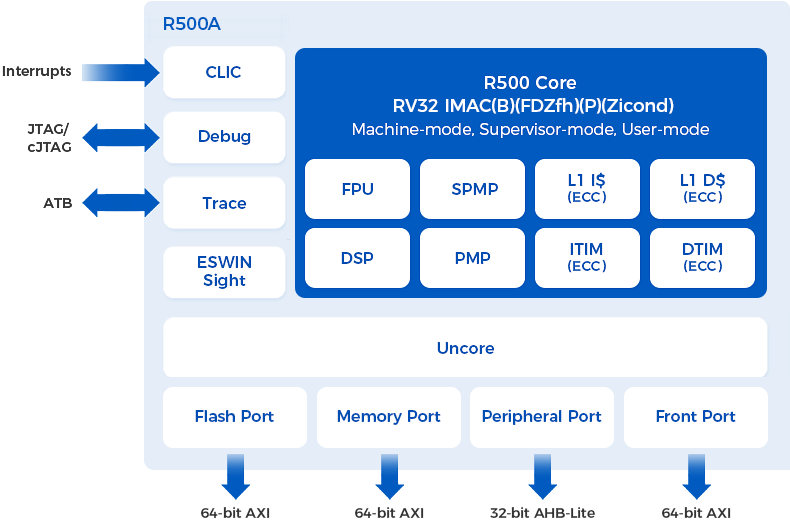

RV32GCBP命令セットをサポートしており、以下の公式拡張機能にも対応しています: Zfh(半精度浮動小数点演算)、Zicbom(キャッシュ操作)、Zicond(条件付き実行)、Zicsr(CSRの読み書き)、Zifence(命令フェンス)、SmePMP(強化型メモリ保護機能)、SPMP(スーパーバイザーモード用メモリ保護機能)、SBA(システムバスアクセス)など。

PPMA(プログラマブルアドレス属性チェック)、Stack Monitor(スタックモニタリング)、ESWIN Sight(内部信号の可視化)、N-Traceなどの機能をサポートしています。

キャッシュコヒーレンシ機能にも対応しており、一部の使用シナリオにおけるキャッシュ一貫性の要求に対応するため、Front Port経由で外部デバイスがDキャッシュ(DCache)へアクセスすることが可能です。

複数の機能安全メカニズムに対応しており、レジスタのパリティチェック、バスインタフェース保護、SRAMインタフェース保護、および非セーフティモジュールとの分離をサポートしています。

また、各種リアルタイムオペレーティングシステム(RTOSやμClinuxなど)に対応しており、SPMPをサポートするLinuxオペレーティングシステムとの互換性も備えています。

本製品は、割り込み処理速度に対する高い要求を持つ設計に適しており、産業用制御、医療機器制御、ストレージ機器制御、モデム、5G通信、ストリーミング伝送などの分野に広く応用されています。特に、車載ECU/DCUや車載グレードICの設計分野において高い適用性を有しています。

| 特徴 | 説明 | ||||

| 命令セットアーキテクチャ | RISC-V 32-bit IMAC(B)(FDZfh)(P)_Zicsr_Zifencei_Zicbom_(Zicond) | ||||

| パイプライン | 6段スーパースカラ順序型デュアルイシューパイプライン、分岐予測器付き | ||||

| 動作モード | マシンモード、スーパーバイザーモード、ユーザーモード | ||||

| セキュリティ | PMP保護領域:最大16個、SPMP保護領域:最大16個; PPMA(プログラマブル物理メモリアトリビュート)チェックに対応 | ||||

| 命令密結合メモリ (ITIM) | 構成可能サイズ:0〜16MB、ECCオプションあり | ||||

| データ密結合メモリ (DTIM) | 構成可能サイズ:0〜16MB、ECCオプションあり | ||||

| L1命令キャッシュ(L1 I$) | 0〜128KB構成可能、 2ウェイ・セットアソシアティブ、32バイトのキャッシュライン構成、ECC対応はオプション | ||||

| L1データキャッシュ(L1 D$) | 0〜128KB構成可能、 4ウェイ・セットアソシアティブ、32バイトのキャッシュライン構成、ECC対応はオプション | ||||

| 割り込み機能 | CLIC割り込みコントローラ対応、最大1008個の高速割り込みサポート リカバリ可能なノンマスカブル割り込み(NMI)に対応 |

||||

| 浮動小数点演算ユニット(FPU) | 倍精度・単精度・Zfh(半精度浮動小数点)拡張をサポート | ||||

| デジタル信号処理ユニット(DSP) | SIMD(シングル命令・マルチデータ)命令およびRISC-V RV32P拡張をフルサポート | ||||

| デバッグ・トレース機能 | デバッグモジュール:JTAG/cJTAG、SBA(System Bus Access)対応 トレースモジュール:RISC-V N-Trace対応 |

||||

| バスインタフェース | 1.フラッシュポート(Flash Port):64ビットの読み取り専用AXIマスタインタフェース 2. メモリポート(Memory Port):64ビットAXIマスタインタフェース 3.ペリフェラルポート(Peripheral Port):32ビットAHB-Liteマスタインタフェース 4.フロントポート(Front Port):64ビットAXIスレーブインタフェース、外部ホストによるITIMおよびDTIMにアクセス用 |

||||

| CoreMark(CoreMarks/MHz) | 5.79 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 2.55 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号