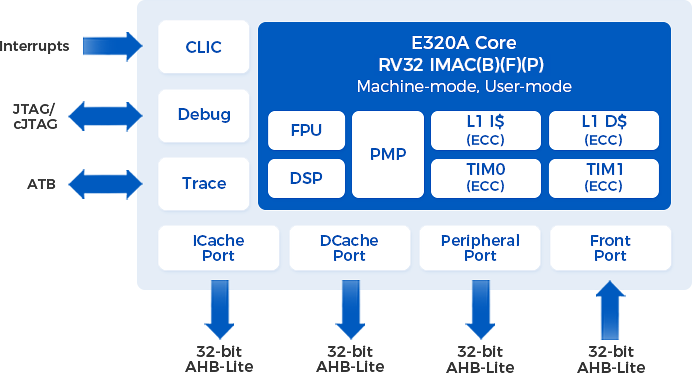

ベースとなる E320 プロセッサに、Parity/ECC および SPM(スタックポインタモニタ)モジュールを追加することで、ASIL-B 機能安全規格に準拠しています。

| 特徴 | 説明 | ||||

| 命令セットアーキテクチャ | RISC-V 32-bit IMAC(B)(F)(P)_Zicsr_Zifencei_Zicbom | ||||

| 動作モード | マシンモード(Machine-mode)、ユーザーモード(User-mode) | ||||

| セキュリティ | Smepmp に対応し、0~16個の物理メモリ保護領域(PMP Region)の構成が可能 | ||||

| パイプライン | 3段パイプライン構成 | ||||

| プロセッサ内部メモリ | TIM0 および TIM1 を内蔵、構成可能サイズ:0KB〜128MB、ECC オプション対応 | ||||

| L1命令キャッシュ(L1 I$) | 構成可能サイズ:4KB〜128KB、Parity / ECC オプション対応 | ||||

| L1データキャッシュ(L1 D$) | 構成可能サイズ:4KB〜128KB、Parity / ECC オプション対応 | ||||

| 割り込み機能 | CLIC割り込みコントローラ対応、最大496個の高速割り込みサポート ノンマスカブル割り込み(NMI)に対応 | ||||

| デバッグ・トレース機能 | デバッグモジュール:JTAG / cJTAG 対応 トレースモジュール:RISC-V N-Trace 対応 |

||||

| バスインタフェース | 1.命令キャッシュポート:32ビット AHB-Lite マスタインタフェース 2.データキャッシュポート:32ビットの AHB-Lite マスタインタフェース 3.ペリフェラルポート(Peripheral Port):32ビット AHB-Lite マスタインタフェース 4.フロントポート(Front Port):32ビット AHB-Lite スレーブインタフェース |

||||

| CoreMark(CoreMarks/MHz) | 4.45 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 1.74 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号