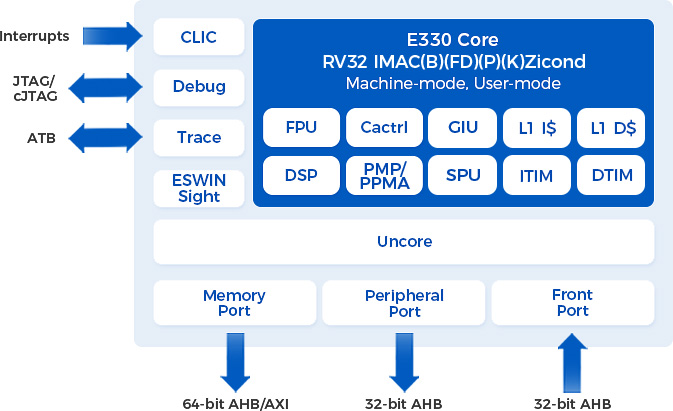

RISC-V 32ビット命令セット IMACB(FD)(P)(K)に対応しており、さらに以下の拡張機能もサポートしています:Zicond条件付き実行拡張、Zicbomキャッシュ操作拡張、Smepmpセキュリティ拡張(埋込み向け物理メモリ保護)、Zilsdロードストア拡張、CIE協調プロセッサインターフェース。

ESWIN Sight機能に対応しており、波形デバッグツールを提供することで、ユーザーがCPU内部の状態や事件を簡単に把握できます。

6段スーパースカラパイプラインおよび分岐予測器を搭載し、幅広い高性能組込みアプリケーションのニーズに対応可能です。

| 特徴 | 説明 | ||||

| 命令セットアーキテクチャ | RISC-V 32-bit IMAC(B)(FD)(P)(K)_Zicsr_Zifencei_Zicbom_Zicond_Zilsd_xewcieに対応 | ||||

| 動作モード | マシンモード、ユーザモードに対応 | ||||

| セキュリティ | 物理メモリ保護(PMP)に対応、最大16領域まで設定可能 PPMAチェック機能に対応 | ||||

| パイプライン | 6段の順序実行スーパースカラパイプライン、分岐予測器付き | ||||

| プロセッサ内部メモリ | ITIMおよび DTIMをサポート、サイズは 0KB〜128MB で設定可能 | ||||

| L1命令キャッシュ(L1 I$) | 容量設定可能(4KB〜128KB) | ||||

| L1データキャッシュ(L1 D$) | 容量設定可能(4KB〜128KB) | ||||

| 割り込み制御 | CLIC割り込み制御装置に対応、最大496個の割り込み要求に対応、ノンマスカブル割り込み(NMI)にも対応 | ||||

| デバッグ/トレース機能 | デバッグモジュール:JTAG / cJTAG に対応 トレースモジュール:RISC-V N-Trace に対応 |

||||

| バスインタフェース | 1. メモリポート:64ビット AHB / AXI マスターインターフェース 2. ペリフェラルポート:32ビット AHB マスターインターフェース 3. フロントポート:32ビット AHB スレーブインターフェース、外部から TIM0・TIM1 にアクセス可能 |

||||

| CoreMark(CoreMarks/MHz) | 5.77 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 2.48 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号