32個の汎用レジスタを搭載しており、より優れた性能を実現しています。

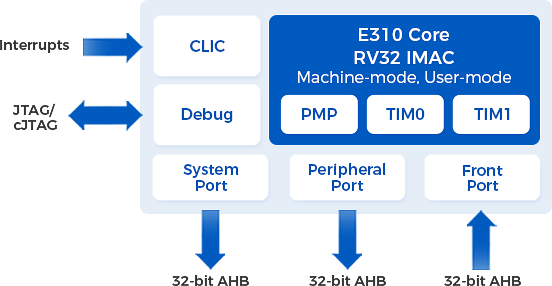

命令やデータの格納に使用できる 2つのオプションの緊密結合メモリ(TIM) をサポートし、外部ホストからのフロントポート経由のアクセスにも対応しています。

Smepmp セキュリティ拡張機能に対応しております。

| 特徴 | 説明 | ||||

| 命令セットアーキテクチャ | RISC-V 32-bit IMAC_Zicsr_Zifenceiに対応 | ||||

| 動作モード | マシンモード、ユーザモードに対応 | ||||

| セキュリティ | オプションで 0〜16個の物理メモリ保護領域(PMP)に対応 | ||||

| パイプライン構成 | 3段パイプライン | ||||

| プロセッサ内部メモリ | TIM0 および TIM1 に対応、容量はオプションで 0KB〜128MB で設定可能 | ||||

| 割り込み制御 | CLIC割り込み制御装置に対応、最大112個の割り込み要求(IRQ)に対応、ノンマスカブル割り込み(NMI)にも対応 | ||||

| デバッグ機能 | デバッグモジュール(Debug Module)は JTAG / cJTAG に対応 | ||||

| バスインタフェース | 1. システムポート(System Port):32ビット AHB マスターインターフェース 2. ペリフェラルポート(Peripheral Port):32ビット AHB マスターインターフェース 3. フロントポート(Front Port):32ビット AHB スレーブインターフェース(外部から TIM0 / TIM1 にアクセス可能) |

||||

| CoreMark(CoreMarks/MHz) | 3.58 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 1.59 | ||||

京公网安备 11030102011303号

京公网安备 11030102011303号